RISC-V is an open standard instruction set architecture (ISA) based on established reduced instruction set computer (RISC) principles. Unlike most other ISA designs, RISC-V is provided under royalty-free open-source licenses. Many companies are offering or have announced RISC-V hardware; open source operating systems with RISC-V support are available, and the instruction set is supported in several popular software toolchains.

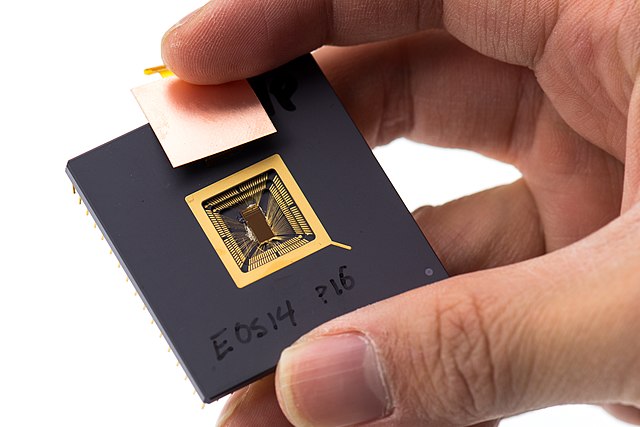

RISC-V processor prototype, January 2013

First Raven1 bring up ST28nm at Berkeley Wireless Research Center (BWRC) June 2012

Reduced instruction set computer

In electronics and computer science, a reduced instruction set computer (RISC) is a computer architecture designed to simplify the individual instructions given to the computer to accomplish tasks. Compared to the instructions given to a complex instruction set computer (CISC), a RISC computer might require more instructions in order to accomplish a task because the individual instructions are written in simpler code. The goal is to offset the need to process more instructions by increasing the speed of each instruction, in particular by implementing an instruction pipeline, which may be simpler to achieve given simpler instructions.

The Sun Microsystems UltraSPARC processor is a type of RISC microprocessor.

An IBM PowerPC 601 RISC microprocessor

RISC-V prototype chip (2013)